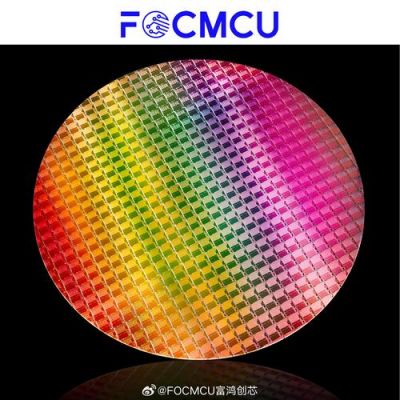

在全球半导体行业的技术竞赛中,台积电作为市场领导者,继续在工艺发展上迈出重要步伐。近日,台积电在北美技术论坛上首次公开了其最新N2 2nm工艺的缺陷率(D0)情况,引起了业内的广泛关注与热议。根据公司发布的信息,N2工艺的缺陷率显著优于历代主流工艺,包括7nm、5nm和3nm等,标志着台积电在先进制程技术上的又一重大突破。

虽然台积电并未透露具体的缺陷率数据,但公司通过展示不同技术节点缺陷率随时间变化的趋势图,强调了N2工艺的卓越表现。在半导体制造中,缺陷率的高低直接关系到芯片良品率的高低,进而影响到生产成本与市场竞争力。过去的经验表明,N7/N6工艺在试产期间的缺陷率最高,而N3/N3P工艺自量产之初就展现出较低的缺陷率,N5/N4工艺更是在试产阶段就表现良好。由此若N2能够延续N5/N4的良好趋势,其未来的发展前景将极为光明。

台积电表示,目前已经在N2工艺下流片的芯片数量大幅增加,这也是其能够快速降低缺陷率的重要因素之一。随着产能的逐步扩大和技术的不断优化,N2工艺将在不久的未来为客户提供更高质量和更高性能的芯片产品。这种快速流片的能力不仅为客户提供了迅效的服务,还展示了台积电在工艺成熟度与生产效率上的强大实力。

在现代计算机技术迅速发展的背景下,2nm工艺的突破将推动整体技术生态的进步。随着物联网、人工智能和5G等新兴应用的快速发展,市场对高性能低功耗芯片的需求愈来愈迫切,而N2工艺正好满足了这一需求。台积电的最新工艺可以实现更高的晶体管密度,显著提升计算性能的同时降低能源消耗,从而为各种应用场景提供了强有力的技术支持。

值得一提的是,台积电在N2工艺的开发过程中,并没有忽视对环境的考量。公司积极推进绿色制造工艺,致力于在降低缺陷率和提升生产效率的同时,减少生产过程中对环境的影响。这一措施不仅提升了企业的社会责任形象,也为后续的可持续发展奠定了基础。

在全球半导体市场竞争愈发激烈的情况下,台积电通过持续的技术创新和质量管理,进一步巩固了其市场领先地位。从N2工艺的表现来看,台积电在小尺寸、高集成度的芯片生产路径上已走在了行业前列。随着客户对4G和5G技术的全面部署和5G应用市场的不断扩展,N2工艺的推出将为芯片产品赋予更加强大的能力。

在未来,台积电不仅需要继续保持在工艺技术方面的领先,同时还需关注全球经济技术变化带来的挑战。例如,贸易政策的不确定性、芯片供应链的安全性以及技术标准的不断进化,都可能影响半导体产业的发展方向。台积电将持续增强其创新能力,构建全面的研发体系,以把握市场机遇,推动整个行业的快速发展。

台积电首次披露N2 2nm工艺的缺陷率,展现了其在半导体制造领域的先进技术与强大实力。随着技术的不断进步和应用需求的日益增长,N2工艺必将为各类科技产品的创新赋予新的活力,未来的市场潜力无可限量。台积电的这一进步不仅将提升自身的竞争能力,也为整个行业的技术进步注入新的动力,助力全球科技的进一步发展。